- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Couches épitaxiales : la base des dispositifs semi-conducteurs avancés

Figure 1 : illustre la corrélation entre les concentrations de dopage, l'épaisseur de la couche et la tension de claquage pour les dispositifs unipolaires.

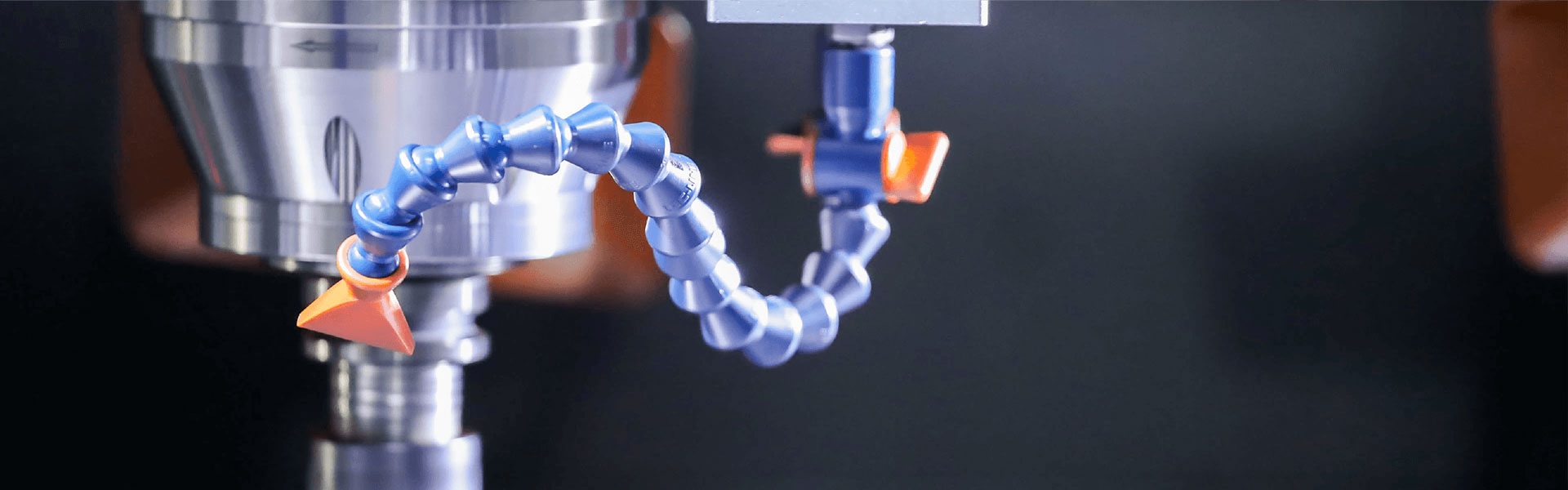

La préparation de couches épitaxiales de SiC englobe principalement des techniques telles que la croissance par évaporation, l'épitaxie en phase liquide (LPE), l'épitaxie par faisceau moléculaire (MBE) et le dépôt chimique en phase vapeur (CVD), la CVD étant la méthode prédominante pour la production de masse dans les usines.

Tableau 1 : Fournit un aperçu comparatif des principales méthodes de préparation de couches épitaxiales.

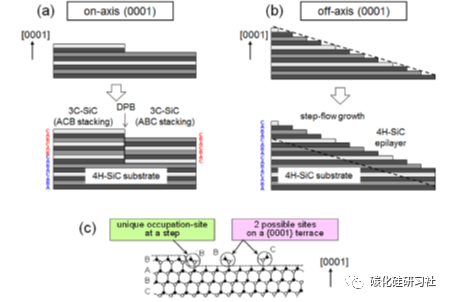

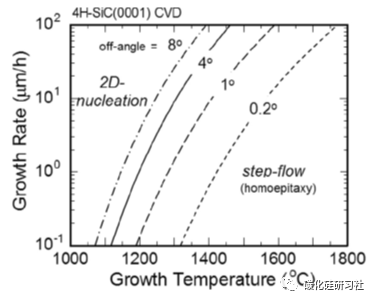

Une approche révolutionnaire implique la croissance sur des substrats {0001} hors axe à un angle d'inclinaison spécifique, comme illustré sur la figure 2 (b). Cette méthode augmente considérablement la densité des pas tout en réduisant la taille des pas, facilitant la nucléation principalement au niveau des sites de regroupement des étapes et permettant ainsi à la couche épitaxiale de reproduire parfaitement la séquence d'empilement du substrat, éliminant ainsi la coexistence de polytypes.

Figure 2 : Démontre le processus physique d’épitaxie contrôlée par étapes dans 4H-SiC.

Figure 3 : Montre les conditions critiques pour la croissance CVD en épitaxie contrôlée par étapes pour le 4H-SiC.

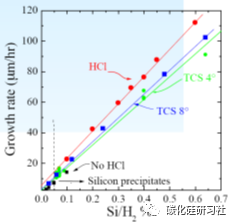

Figure 4 : Compare les taux de croissance sous différentes sources de silicium pour l’épitaxie 4H-SiC.

Dans le domaine des applications basse et moyenne tension (par exemple, appareils 1 200 V), la technologie d'épitaxie SiC a atteint un stade de maturité, offrant une uniformité relativement supérieure en termes d'épaisseur, de concentration de dopage et de répartition des défauts, répondant de manière adéquate aux exigences des SBD basse et moyenne tension. , MOS, appareils JBS et autres.

Cependant, le domaine de la haute tension présente encore des défis importants. Par exemple, les dispositifs évalués à 10 000 V nécessitent des couches épitaxiales d'environ 100 μm d'épaisseur, mais ces couches présentent une épaisseur et une uniformité de dopage considérablement inférieures à celles de leurs homologues basse tension, sans parler de l'impact néfaste des défauts triangulaires sur les performances globales du dispositif. Les applications haute tension, qui tendent à favoriser les dispositifs bipolaires, imposent également des exigences strictes en matière de durée de vie des porteurs minoritaires, ce qui nécessite une optimisation des processus pour améliorer ce paramètre.

Actuellement, le marché est dominé par les plaquettes épitaxiales SiC de 4 et 6 pouces, avec une augmentation progressive de la proportion de plaquettes épitaxiales SiC de grand diamètre. La taille des plaquettes épitaxiales SiC est fondamentalement déterminée par les dimensions des substrats SiC. Avec les substrats SiC de 6 pouces désormais disponibles dans le commerce, la transition de l'épitaxie SiC de 4 pouces à l'épitaxie SiC de 6 pouces est en cours.

À mesure que la technologie de fabrication des substrats SiC progresse et que les capacités de production augmentent, le coût des substrats SiC diminue progressivement. Étant donné que les substrats représentent plus de 50 % du coût des plaquettes épitaxiales, la baisse des prix des substrats devrait entraîner une baisse des coûts de l'épitaxie SiC, promettant ainsi un avenir meilleur pour l'industrie.**